汽车行业正在经历一场历史上前所未有的革命。汽车中摄像头、激光雷达和雷达等传感器的激增导致了先进的驾驶员辅助系统(ADAS)的出现,这些系统在自主性、安全性和性能方面为现代车辆提供了前所未有的功能。

然而,随着传感器活动的增加,该行业在硬件、计算和设计方面也面临着重大挑战。具体来说,这些传感器产生的数据量在数据管理、控制和处理方面产生了问题。同时,要实现性能和安全性,需要对这些数据进行实时、低延迟的处理。

所有这些因素都导致人们意识到通用计算硬件不再能够胜任这项任务。为了实现最高水平的车辆自主性,该行业已转向硬件加速和定制电子产品,以取代现成的组件。虽然ASIC提供了最高的性能和最低的功耗,但如果设计要求发生变化,它们就不允许有任何灵活性。此外,与基于FPGA的解决方案相比,ASIC的开发周期较长。

在当今快速和动态的世界中,该行业需要的硬件不仅要支持加速,而且要足够灵活,以跟上不断变化的算法和传感器技术。这种所需的灵活性可以通过ASIC/SoC与嵌入式FPGA(eFPGA)技术的结合来实现,这是一种独特的解决方案,有望实现ADAS的未来。

Achronix解决方案

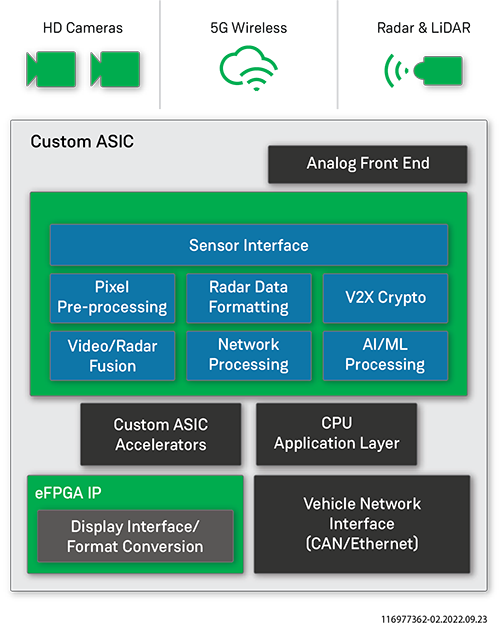

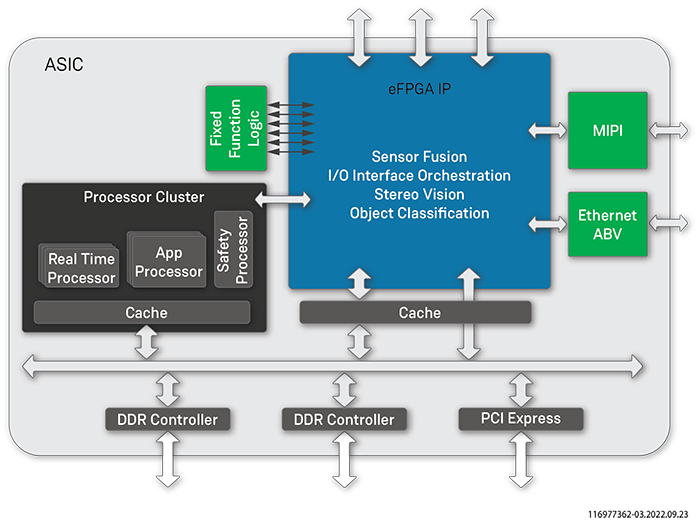

当涉及到为ADAS设计硬件时,挑战在于支持所需的大量应用程序和接口。从高层来看,ADAS计算引擎将首先严重依赖其传感器接口。现代车辆配备了多个高通量传感器,需要计算硬件能够通过传感器融合过程快速可靠地解释、管理和控制数据流。从硬件的角度来看,传感器融合需要计算块与外部高速接口以及设备内的数据路由具有超高带宽连接。

支持ADAS应用程序的定制SoC

其次是传感器融合,通信作为一个整体是ADAS的一个关键方面。CAN和以太网等协议的车辆网络接口,以及对5G等无线通信标准的支持,对系统提出了独特的计算要求。

除了通信之外,所需的特定于应用程序的任务可能非常多样化。从驾驶性能的角度来看,单个ADAS解决方案通常依赖于许多独特的任务,如像素预处理、数据格式化和AI/ML处理。从安全的角度来看,加密引擎也是ADAS的必要条件,因为敏感的用户数据可能会通过车联网(V2X)受到损害。最后,用户体验(UX)是ADAS的关键要素,其中显示接口和格式转换是提供信息娱乐显示的必要过程,通过ADAS实现创造自然直观的用户体验。

这些任务中的每一项对ADAS实施的整体性能都同样重要,但每项任务都有独特的计算要求,这些要求并不总是相互重叠。为了支持这些不同的需求,系统架构师通常会开发专有的SoC,允许为每个给定的应用程序优化多个专用硬件块,从而确保整体高性能。

eFPGA优势

ADAS的一个决定性特征是需要快速处理,以实现近乎实时的决策——这些决策可能意味着车辆乘客的生死存亡。因此,ADAS实现中的底层计算需要极其强大的处理能力和尽可能低的延迟。同时,在考虑电动汽车(EV)时,设计人员也会遇到对低功耗处理的严格要求,以尽可能延长车辆电池寿命。这种低延迟、低功耗处理的独特组合使ADAS成为一个特别具有挑战性的领域。

幸运的是,FPGA特别适合满足这些要求,使其成为理想的硬件加速器,减轻了ADAS所依赖的计算密集型机器学习算法的负担。与基于CPU和GPU的系统相比,这提高了处理速度和功耗。后者是FPGA真正闪耀的地方,因为FPGA的每瓦性能比替代品更好。

FPGA在汽车设计中的价值早已确立,因为在过去的15年里,该技术已被用于2亿多辆汽车。然而,超越FPGA,很明显,对于当今ADAS的需求,eFPGA占据了主导地位。

eFPGA与离散FPGA解决方案的比较

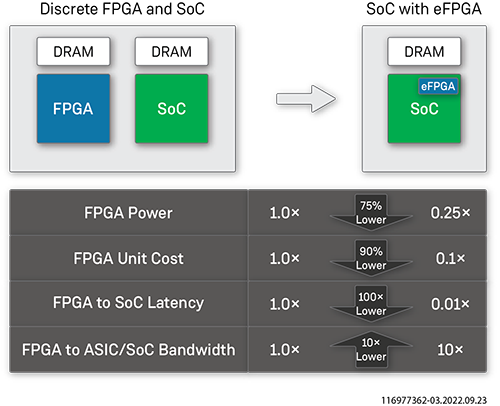

与独立FPGA相比,eFPGA IP在ADAS应用中的真正价值主张是它能够集成在SoC中,并根据团队的确切资源需求进行调整。eFPGA实例通过消除独立FPGA的多余功能,增加了灵活性,同时降低了系统成本、功耗和电路板空间,这些功能在进入大批量生产时是不需要的。此外,集成eFPGA IP使设计人员能够实现FPGA结构与其他SoC资源(如嵌入式CPU或专用接口)的紧密耦合。正是这种紧密耦合和消除了高功耗的I/O,使eFPGA能够提供前所未有的性能和节能,而不是将独立的FPGA用作SoC的侧车。

在SoC中嵌入eFPGA实例提供了其他重要优势,例如通过OTA软件更新在现场更新算法的能力。此外,eFPGA有助于减少BOM,与独立的FPGA解决方案相比,eFPGA可能为ADAS设计人员提供80%-90%的整体系统成本。

Achronix ADAS产品

Achronix Speedcore eFPGA IP 提供了一种独特的架构,融合了许多可以提高性能、降低功耗和减少芯片面积的功能。在指定Speedcore eFPGA实例时,设计人员可以选择架构元素的最佳组合,包括:

- 逻辑–6输入查找表(LUT)加上集成的宽MUX功能和快速加法器

- 逻辑RAM——LRAM2k每个存储块2 kb,LRAM4k每个存储块4 kb

- 块RAM——BRAM72k每个存储块72 kb,BRAM20k每个存储块20 kb

- DSP64-18×27乘法器、64位累加器和每个块27位预加法器

- 机器学习处理器(MLP)-每个块32个乘法器/累加器(MAC),支持整数和浮点格式

基于Speedcore的ADAS SoC

在大多数情况下,汽车设计师需要大规模生产他们的SoC,以支持每年销售的大量车辆。Speedcore eFPGA是当今市场上为数不多的经过大量生产验证的可嵌入织物之一,迄今为止,我们的客户已成功交付了超过1500万台采用我们Speedcore技术的设备。

除了支持大批量生产的能力外,我们的Speedcore知识产权还得到了我们提供的一整套工具和产品的支持。对于设计师来说,我们在开发我们的独立FPGA时利用了我们的经验 Achronix工具套件 该套件本身配备了Achronix专有的ACE设计工具以及Synopsys的Synplify Pro合成工具。其他工具包括Snapshot窗口、实时设计调试工具以及许多Achronix特定的仿真库。总之,Achronix工具套件是超过15年工具开发和改进的结晶。

将经过硅验证的工具与经过生产验证的eFPGA IP相结合,为ADAS设计师提供电源解决方案。

了解更多关于Achronix在ADAS应用中的信息

要了解更多关于FPGA和eFPGA IP如何在ADAS中实现前所未有的性能,请访问: