采用Speedcore eFPGA IP构建的小芯片

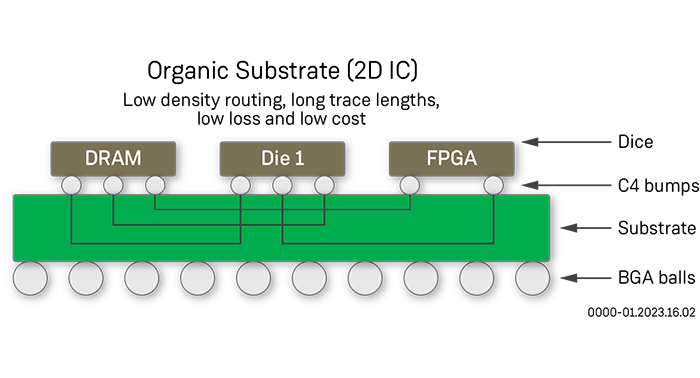

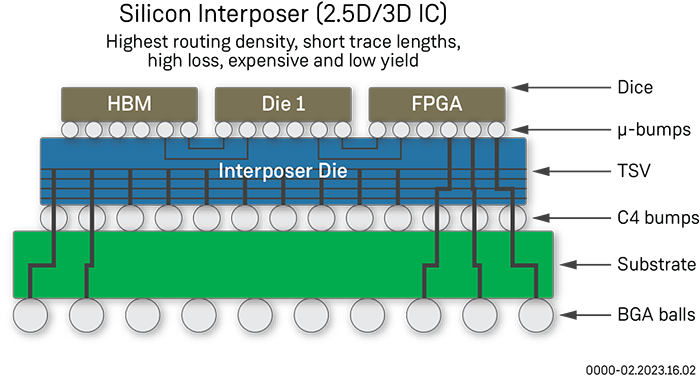

Speedcore™eFPGA IP 可以以各种形式部署,包括集成到客户定义的小芯片中,该小芯片可以通过2.5D互连技术部署在系统级封装(SiP)解决方案中。下图显示了SiP集成的三个选项。第一种基于提供最低成本但不提供管芯之间最高互连密度的有机基板。基于再分布层(RDL)的中介层是互连密度的下一步,但也更昂贵。最后,硅基中介层提供了最高的互连密度和与高带宽存储器(HBM)的兼容性,但成本最高。

与独立的FPGA解决方案相比,小芯片解决方案允许设计人员减少所需的电路板空间,并实现新的集成可能性。使用基于Speedcore eFPGA IP的定制小芯片解决方案,设计人员需要指定小芯片与其ASIC芯片之间的互连技术。Speedcore eFPGA IP与小芯片互连技术无关,其互连密度和性能可用于所有各种2.5D互连。设计人员可以完全定制Speedcore eFPGA中的逻辑、DSP块和内存的数量,以满足他们的应用需求。

Speedcore eFPGA小芯片SiP示例

具有Speedcore eFPGA IP的小芯片与裸FPGA芯片集成的优势

传统上,想要开发集成ASIC和FPGA解决方案的设计人员需要从FPGA供应商那里购买裸片,但这种方法存在挑战:

- FPGA供应商通常不支持裸片业务,因为它需要定制处理和测试

- 独立FPGA通常没有系统级封装集成所需的I/O结构

- 独立FPGA没有针对这些类型的应用进行优化,这导致了过高的功耗、更大的封装要求和管芯间带宽限制

另一方面,通过使用基于Speedcore eFPGA IP构建的小芯片,设计人员可以实现以下好处:

- 通过仅包含其应用所需的特定功能,降低功耗和成本

- 优化了小芯片和ASIC之间的接口,以最小的延迟获得最大的带宽

- 基于尺寸优化的eFPGA IP小芯片的更小外形封装

Speedcore eFPGA IP芯片与单片eFPGA和ASIC集成的优势

寻求最高集成度的设计师可以选择开发包含Speedcore eFPGA IP的单片ASIC(单芯片)。然而,在某些应用中,单片集成不允许使用基于小芯片的方法实现产品灵活性。

通过使用基于eFPGA IP的小芯片,设计人员可以实现与单片eFPGA ASIC解决方案相比的优势,例如:

- 公司可以在不需要FPGA灵活性的情况下,在没有FPGA小芯片的情况下创建成本更低、功耗更低的独特产品解决方案(不同的SKU)。

- 在ASIC的最佳工艺技术不适合嵌入式FPGA的情况下,支持不同的工艺技术。例如,使用混合信号技术构建的ASIC或基于eFPGA IP不可用的技术构建的ASICs。

Speedcore eFPGA IP芯片入门

用于开发Speedcore eFPGA IP小芯片的设计过程与开发具有嵌入式Speedcore eFPGA IP的ASIC相同。这种经过验证的设计流程使开发利用既定工具和流程的Speedcore eFPGA IP小芯片解决方案变得容易。为了开始使用基于Speedcore eFPGA的小芯片, 立即联系Achronix.