如今,先进驾驶辅助系统(ADAS)处理器市场以每年25%以上的速度增长。这一增长是由ADAS功能(包括自动紧急制动、变道辅助和自适应巡航控制功能)从豪华车向中端甚至入门级车辆的迁移推动的。到下一个十年中期,ADAS功能将几乎普及。2018年,几家制造商提供了配备自动驾驶平台的车辆,这些平台提供了优于2级的自动驾驶能力,包括通用汽车的Super Cruise、梅赛德斯-奔驰的Distronic Plus、日产的ProPilot Assist和特斯拉的Autopilot。

正如前文所述这篇博客文章的第一部分Achronix预计,未来备受青睐的自动驾驶架构将越来越去中心化,但集中式和去中心化的架构设计方法都需要硬件加速,其形式比目前实现的要多得多。无论是集中式还是分散式,自动化和自动驾驶系统的预期计算架构显然都是异构的,需要混合处理资源,用于从局域网控制、翻译和桥接到基于神经网络上运行的深度学习算法的并行对象识别等复杂任务。因此,目前豪华无人驾驶汽车中的100多个CPU很容易膨胀到几百个CPU和其他处理元件,用于更先进的自动驾驶汽车。

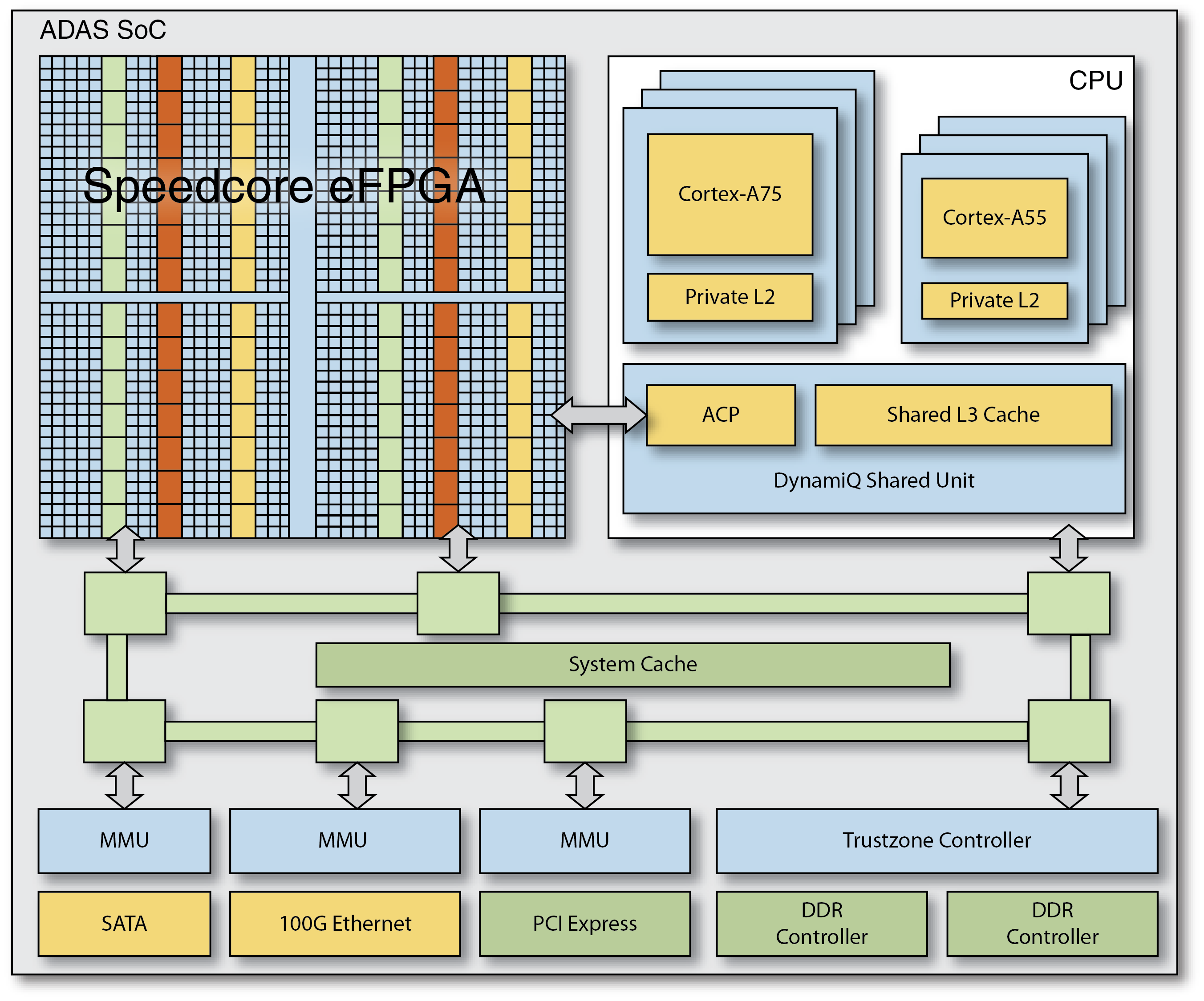

Achronix的Speedcore eFPGA IP可以集成到针对自动驾驶汽车应用的ASIC或SoC中,以提供定制的可编程结构,提供硬件级处理性能。Speedcore eFPGA IP提供了应对这些自动驾驶汽车系统中发生的快速进化变化所需的硬件可编程性和可重新编程性。

为了将Speedcore eFPGA IP集成到他们的ASIC和SoC中,设计人员指定了所需的逻辑、内存和DSP资源,Achronix配置了一个满足这些要求的定制Speedcore IP块。Speedcore查找表(LUT)、RAM块和机器学习处理器(MLP——Speedcore Gen4架构的新功能)可以像构建块一样组装,为任何给定的应用程序创建最佳的可编程结构。

将Speedcore eFPGA IP集成到ASIC或SoC中增加了独特的设计优势,包括:

- 可编程硬件资源,允许快速更改以硬件速度运行的算法。

- eFPGA中的资源可以配置为可编程卸载引擎,以处理尚未标准化但仍必须以硬件速度执行的复杂算法。

- 消除ASIC/SoC旋转,实现半代甚至全代增强。

- 以安全和加密引擎的形式提供更高的安全性,可以根据需要进行修改或升级。

- 如果需要,能够对系统设计进行重大的远程更新。

- 可编程硬件资源,例如,可用于实现枚举can总线所需的可编程BIST引擎。当不需要BIST功能时,可以重用这些资源来实现其他功能。

在未来先进的全自动驾驶汽车中,数十甚至数百个分布式CPU和众多其他处理元件的存在是有保证的。外围传感器融合和其他处理任务可以由ASIC、SoC或传统FPGA完成。但是,嵌入式FPGA块的引入,如Achronix Speedcore eFPGA IP,在更短的延迟、增强的安全性、更大的带宽和更好的可靠性方面提供了许多系统设计优势,这在使用CPU、GPU甚至独立FPGA时根本不可能实现。

有关此主题的深入了解,请参阅Achronix白皮书,标题为如何满足使用Speedcore eFPGA的自动驾驶汽车系统的功率、性能和成本(WP015).