| 博客图标 | 博客标题 | |

|---|---|---|

|

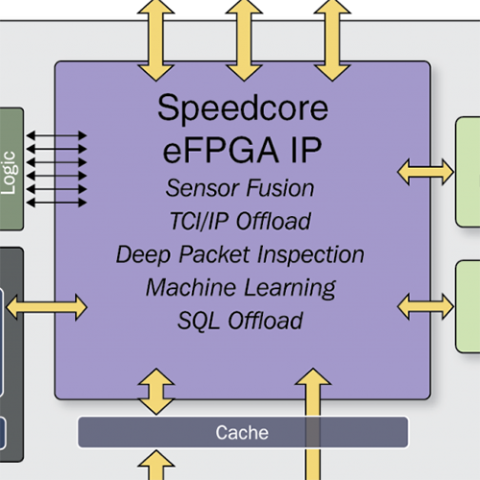

Speedcore eFPGA作为风险缓解工具– 阿洛克·桑加维, 高级营销经理系统架构师和项目经理担心如何在开发SoC时降低风险。风险可以以多种形式出现,但最常见的是定义不清和不断变化的标准以及需要面向未来的设计。 |

> |

|

将机器学习从云端转移需要eFPGA– 阿洛克·桑加维, 高级营销经理人工智能正在重塑我们生活的世界,并在商业和工业系统应用中开辟机会,从自动驾驶和医疗诊断到家用电器、工业自动化、自适应网站和金融分析。接下来是将系统连接在一起的通信基础设施,朝着自动化自我修复和优化的方向发展。例如,美国。 |

> |

|

Speedcore eFPGA增强边缘网络解决方案的安全性– 阿洛克·桑加维, 高级营销经理下一代网络解决方案正在将处理从云端推向网络边缘。同时,围绕可编程逻辑构建的处理结构提供了使计算更加以数据为中心的能力。可编程逻辑使得构建数据管道成为可能,而传统处理器则要求通过复杂的内存缓存层次结构将数据馈送到其管道。 |

> |

|

下一代人工智能硬件需要灵活和可编程– 史蒂夫·门索尔, 营销副总裁人工智能(AI)正在重塑世界的运作方式,在商业和工业系统中开辟了无数机会。应用涵盖了不同的市场,如自动驾驶、医疗诊断、家用电器、工业自动化、自适应网站和金融分析。即使是将这些系统连接在一起的通信基础设施也在朝着自动化自我修复和优化的方向发展。 |

> |

|

2018年国际消费电子展的参观者将体验交通的未来– 阿洛克·桑加维, 高级营销经理当参加2018年国际消费电子展的游客想要前往市中心的拉斯维加斯会议中心时,他们很可能会乘坐Lyft的全自动驾驶汽车前往那里。虽然这次未来主义之旅肯定会是许多骑手的第一次,但这种点对点的旅行很快就会变得司空见惯。但有关自动驾驶汽车安全性的问题仍然存在。在Lyft的CES演示中,一名后备飞行员将坐在驾驶座上,以增加安全性。 |

> |

|

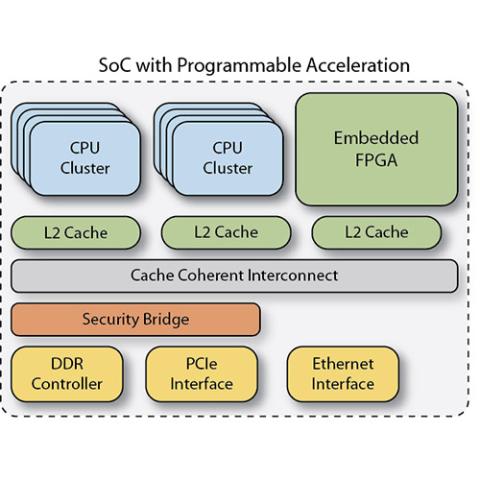

为什么设计人员需要考虑将CPU与FPGA结构相结合– 阿洛克·桑加维, 高级营销经理鉴于该行业开始达到通过进一步缩小工艺几何形状在物理和经济上可以实现的极限,减小特征尺寸和增加晶体管数量不再能达到以前的效果。相反,该行业非常正确地专注于全新的系统架构,并通过彻底反思如何在每个设备中实现任务来更好地利用可用的硅。 |

> |

|

查看我们最近关于eFPGA加速基础的视频– 阿洛克·桑加维, 高级营销经理我们现有的客户向我们提出了一些非常大的问题:“这项技术如何在我的特定流程中实现一步到位的改变 Speedcore IP 是否集成到我的SoC中?如何提高我的ASIC的性能?”我们乐于回答这样的问题。 然而,当我们第一次见到一家对我们的嵌入式FPGA(eFPGA)IP感兴趣的公司时,问题往往很简单,“在最基本的层面上,它能为我做什么?”这个问题可能是我们为他们回答的最重要的问题。 |

> |

|

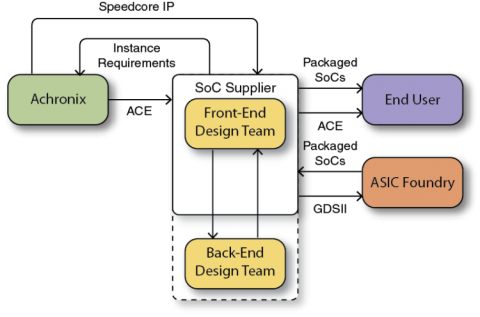

谁是谁在动物园– 史蒂夫·门索尔, 营销副总裁虽然概念eFPGA IP这相当简单,涉及的各方数量及其责任在一开始可能并不明确。eFPGA的可编程特性可能会导致谁负责什么的混淆。对于独立的FPGA,涉及三方:FPGA供应商、代工厂和最终用户。两者之间的关系很简单,也很容易理解。 |

> |

|

回到基础:非专业人士对eFPGA的介绍– 阿洛克·桑加维, 高级营销经理回答什么是 嵌入式现场可编程门阵列 首先,我们必须回答什么是FPGA的问题。 过于简单化。FPGA是一种能够 重新布线 只要有指示,它就会在现场进行内部工作,然后以硬件(而不是软件)的速度运行,直到再次重新布线。这种能力被称为现场可编程性。 |

> |

|

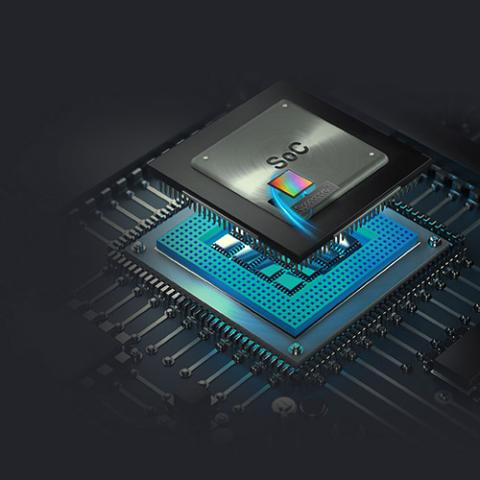

嵌入式FPGA——终极加速器– Kent Orthner, 系统架构师嵌入式FPGA(eFPGA)是一种IP核,您可以将其集成到ASIC或SoC中,以获得可编程逻辑的好处,而无需成本,但具有更好的延迟、吞吐量和功率特性。使用eFPGA,您可以定义查找表(LUT)、寄存器、嵌入式内存和DSP块的数量。您还可以控制纵横比、I/O端口数量,在功耗和性能之间进行权衡。真人百家乐提供Speedcore IP的GDS II表示,您可以直接将其集成到SoC或ASIC中。我们还为您提供了一个定制的、功能齐全的ACE设计工具版本,您可以使用它来设计、验证和编程Speedcore eFPGA. |

> |