新的后比特币加密货币已经开发出来,具有ASIC的阻力,为加密货币矿工创造了公平的竞争环境,如第1部分以及2这个博客。ASIC阻力是为了对抗少数有能力构建ASIC解决方案的实体对加密货币的垄断而开发的,就像比特币一样。然而,ASIC的阻力并不能确保加密货币的必要稀缺性。因此,加密货币算法的开发人员设计了一种额外的方法来从根本上确保稀缺性。它被称为记忆硬度,其可以与ASIC电阻结合。这些新加密货币最突出和最有前景的例子是Monero/XMR和Ethereum/ETH。这些新的加密货币算法既能抵抗ASIC,又难以存储。

使加密货币挖掘算法抗ASIC的一种方法是需要比ASIC更大的硬件来执行算法。例如,需要数GB内存的算法,例如用于以太坊的Equihash算法,是内存硬的。

内存硬度被纳入加密货币挖掘算法,以禁止执行快捷方式,否则这些快捷方式将允许预计算。内存硬加密货币挖掘算法要求挖掘过程必须读取存储在内存位置的值,根据当前算法为该特定加密货币指定的步骤使用该值,然后将结果用作下一个内存事务的地址。因此,无法确定内存地址值先验不同的内存硬算法以略微不同的方式确保了这一特征。

通过内存访问减慢算法速度

内存硬算法通过利用内存事务速度的基本下限来创建高难度的工作量证明例程。这些限制源于物理定律。因此,这些加密货币算法的执行时间不能减少到某个最小值以下。这些内存硬算法保证所有事务必须按顺序进行,因此实现无法通过并行化来加速这一过程。所需的内存事务数量可能达到一百万或更多,这确保了中间结果,因此。最终结果无法预先计算。

内存硬加密货币算法需要数百万个连续的内存事务来执行完整的算法,但这些算法在计算上并不密集。因此,矿工的性能几乎完全取决于内存带宽和事务延迟(即,最短的内存周期时间获胜)。

内存硬度决定了高级加密货币矿工的架构,而这种架构的理想硬件平台取决于算法,因为不同算法的执行性能以不同的方式取决于内存大小和访问模式。

算法要遍历的内存阵列的大小决定了平台的架构。例如,以太坊加密货币算法需要几GB的内存大小,而门罗币算法需要的内存要小三个数量级。这些差异导致了非常不同的内存架构。

理论上,具有较小内存大小要求的算法可以使用外部存储器来实现。然而,由于各种原因,这些算法的效率并不高,主要是因为片上存储器的带宽和延迟比片外存储器快几个数量级。PCB上的功耗和密度是增加使用管芯外存储器的实现的初始和运营成本的其他关键因素。加密货币矿场部署了数千台矿机,因此实现最佳的能效和每单位容量的最高计算性能至关重要。

缓存太大

这些加密货币算法被有意设计为使用太大的内存空间,无法容纳当今大多数微处理器上的二级缓存。算法设计的这一方面迫使处理器在片外进行内存访问。DDR4 SDRAM等外部存储设备速度太慢、太贵、耗电量太大,并且占用了太多的空间来竞争性地执行这些算法。SDRAM是面向块的存储器,因此对于加密货币算法执行的细粒度交易来说效率非常低。

因此,对于需要执行内存硬算法的加密货币矿机来说,PC/服务器CPU和GPU是糟糕的实现工具。使用片上存储器的架构将快得多。此外,GPU在大内存空间中进行稀疏遍历的能力很差,这也是它们是内存硬加密货币挖掘效率低下的引擎的另一个原因。

大型高端FPGA确实以许多中大型嵌入式存储块的形式拥有大量的片上存储器。这一事实似乎使独立FPGA成为内存硬加密货币算法的首选硬件实现。然而,现成的FPGA是为通用应用而设计的。它们根本不是为加密货币挖矿而设计的。

通用FPGA中的片上内存量仍然是严重限制在这些设备上并行运行的挖掘进程数量的主要因素。FPGA内存块均匀且稀疏地分布在FPGA核心上,但这些稀疏的嵌入式内存块单个太小,无法用作内存硬的加密货币挖掘空间。因此,这些较小的嵌入式FPGA存储器必须组合成较大的存储器,这大大降低了整体性能,并使通用FPGA不适合这些算法。

为什么eFPGA是最佳设计解决方案

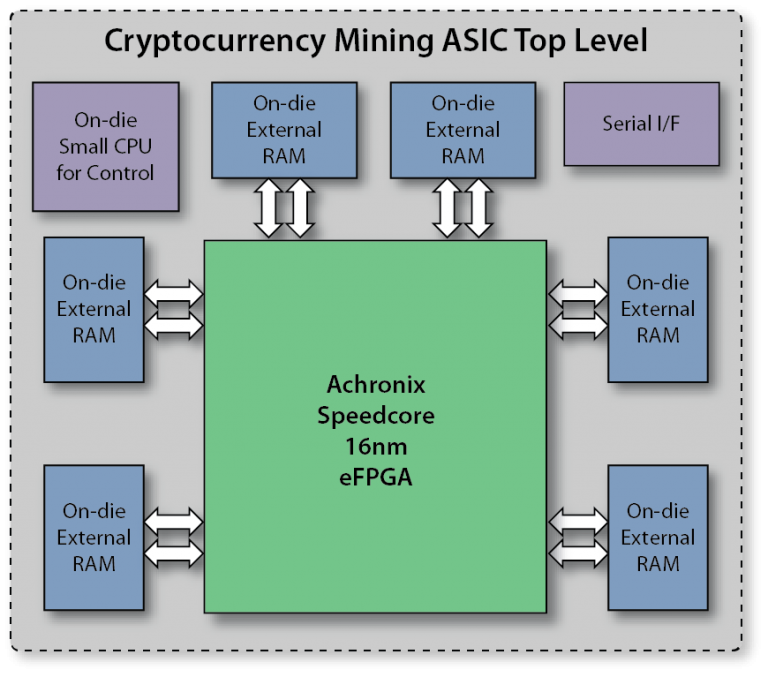

这些新型加密货币矿工的最佳实现技术是具有嵌入式FPGA(eFPGA)阵列的ASIC,这些阵列是专门为实现加密货币挖掘算法而设计的。这种设计解决方案允许采矿设备开发人员在芯片上投入适量的所需硬件资源来实现目标算法,同时能够快速重新配置以响应算法变化。

将ASIC和eFPGA技术相结合,为实现新的加密货币挖掘架构创造了完美的半导体载体。eFPGA允许在底层算法发生变化时对加密货币挖掘引擎进行硬件重新配置,这意味着芯片不需要重新旋转以适应算法变化。由此产生的挖掘芯片只需要通过将新的比特流图像文件远程下载到设备的配置闪存中来重新编程。

嵌入式FPGA能够与紧邻算法执行硬件的多个正确大小的片上存储器紧密集成。与外部存储器(如GPU和CPU)相比,这种使用片上存储器的方式赋予了这种设计解决方案巨大的功率、性能和面积(PPA)优势。借助现代半导体技术节点,现在可以集成这些硬存储算法所需的数兆字节片上SRAM。此外,这是一个ASIC,可以选择最紧凑的存储器配置,与标准FPGA相比,PPA效率要高得多。

您可以使用Achronix的Speedcore eFPGA阵列及其易于定制的特性,精确设计加密货币算法目标类所需的FPGA。在考虑制造和部署数十万或数百万个加密货币挖矿引擎时,这是一个极其重要的经济驱动因素。

本博客基于Achronix白皮书,标题为 使用Achronix Speedcore嵌入式FPGA更快、更快、更便宜地挖掘加密货币 (WP014)。有关此主题的更多信息,请下载完整的白皮书。