当我们小时候开始上学时,我们学到的第一堂课就是如何分享(然后很快就不要拿剪刀跑)。正如我们的系统工程高级总监Kent Orthner今年6月在DAC上讨论的那样,在嵌入式FPGA(eFPGA)的关闭时间方面,共享也是关键。对于Speedcore IP等eFPGA,关闭时序的任务由两个人负责:ASIC设计师,负责主机ASIC中的设计;FPGA设计师,负责针对FPGA的设计。这种情况与使用FPGA的PCB上的时序闭合非常相似,在PCB上,两个设计人员需要合作并共享时序弧(FPGA设计可能会在电路板设计完成后很长一段时间内发生变化)。

使用eFPGA,可编程块可以插入ASIC内的任何位置,这意味着各个eFPGA端口可以连接到ASIC内的其他块,或连接到连接到外部引脚的缓冲器。使该过程更加复杂的是,eFPGA中的设计主机可能会随着时间的推移而变化,可能是在ASIC设计多年后。

但是,Achronix并没有让设计团队开发流程,而是提供了一种明确的方法来实现时间闭合,并支持行业标准的时间分析工具。正如肯特解释的那样(他的演讲视频是 在这里),设计团队可以使用两种计时模型(或模式):简单和高级。

简单模式

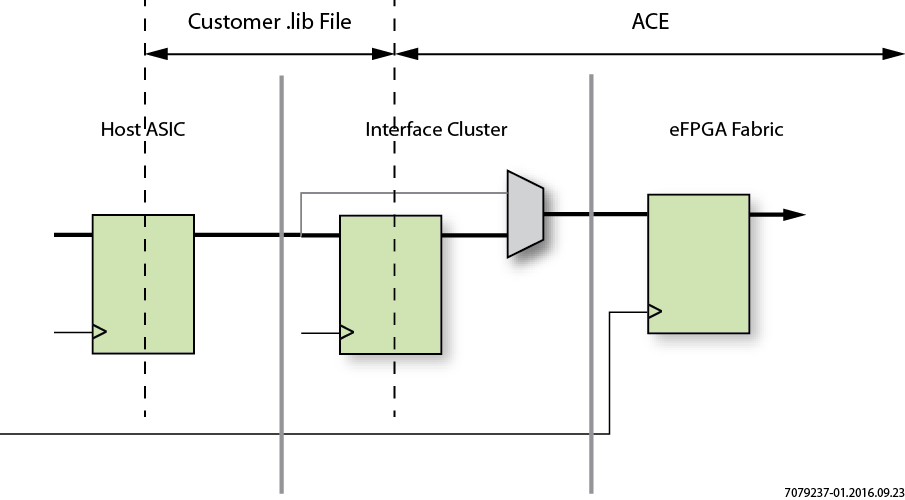

在简单定时模式下,Speedcore实例外部主机ASIC中的IP之间的定时终止于Speedcore边界环中接口集群中的寄存器(如下所示)。在这种情况下,延迟不依赖于Speedcore实例中托管的设计。在简单模式下,SoC供应商使用标准工具(如PrimeTime)执行定时关闭,其中 .lib 文件表示与边界触发器之间的定时数据(设置/保持/时钟到q)。在这种情况下,ACE设计工具可能需要时钟插入延迟信息。

高级模式

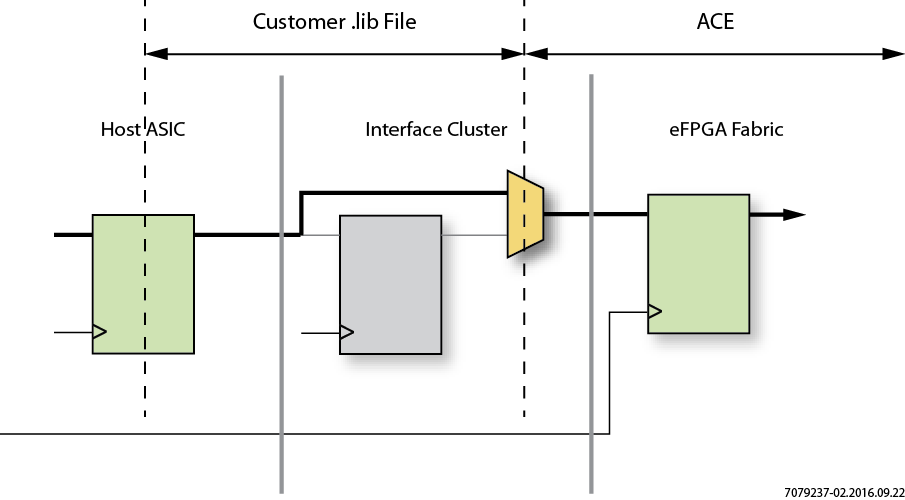

顾名思义,这种情况更为复杂,Speedcore eFPGA和外部IP之间的时序闭合由SoC供应商(如PrimeTime)和ACE设计工具(如下所示)共享。在高级模式下 .lib 文件不包含Speedcore结构中特定触发器的延迟,而是表示一系列触发器,选择这些触发器是为了使用硬件进行定时关闭 .lib 文件与ACE中的定时关闭相关。这个 .lib 文件仍然包含每个引脚的一个setup/hold/clk-to-q值。在这种模式下,最终的时间签核来自ACE,通过使用一套包含代表实际最终用户设计的关键路径的用户设计来完成。

定时闭包是一个迭代过程

正如Kent所解释的那样,定时关闭由一组基本步骤组成:

- 选择一个目标频率,并确定ASIC逻辑将使用(共享)多少时钟周期。

- 使用真人百家乐提供的预算,使用行业标准工具(如PrimeTime)运行ASIC定时关闭

.lib文件夹。 - 提取每条导线上延迟的ASIC部分,并按照真人百家乐提供的模板通过约束文件将其提供给ACE。

- 通过ACE运行一套具有代表性的设计,以确认每个设计都符合时间限制。

- 如果这些设计中的一个或多个无法满足时序要求,请修改FPGA设计或返回步骤1。

额外的好处是,在设计ASIC时不需要选择时序模式,而是由FPGA设计师决定。要了解更多信息,请查看 肯特的视频。