Achronix的每个实例Speedcore eFPGA在ASIC或SoC设计中,必须在系统通电后进行配置,因为Speedcore eFPGA采用非易失性SRAM技术来存储eFPGA的配置位。每个Speedcore实例都包含自己的FPGA配置单元(FCU),用于初始化、配置和管理Speedcore eFPGA的核心逻辑阵列。例如,如果在ASIC/SoC设计中实例化三个Speedcore eFPGA,则芯片上将有三个FCU。每个FCU都有一组配置引脚和一组配置模式引脚,有助于确定配置引脚的操作方式。

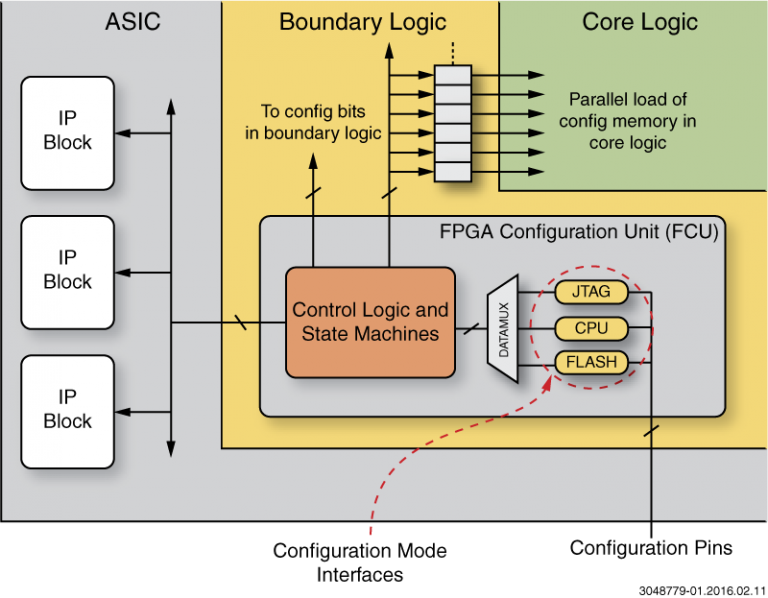

下图显示了ASIC/SoC、包括FCU的Speedcore eFPGA边界逻辑和Speedcore eFPGA核心逻辑之间的关系:

如上图所示,FCU的配置模式引脚为标记为JTAG、CPU和Flash的三个模式相关块供电,这是FCU中可用的三种配置接口。FCU的配置模式引脚以及eFPGA JTAG控制器中基于寄存器的设置决定了配置引脚的操作方式。

配置模式引脚可以单独在CPU和Flash模式之间进行选择。然而,JTAG配置模式独立于配置模式引脚。JTAG模式是通过发送FCU命令来启用的,这些命令在Speedcore eFPGA的JTAG TAP控制器中设置了适当的位。一旦JTAG模式被启用,它就会覆盖配置模式引脚的设置,直到被禁用。该组织允许JTAG控制器控制eFPGA,而不管配置模式设置如何。

这三种配置模式各自具有独特的优势。

CPU配置模式

FCU的CPU配置模式允许外部CPU充当主控器,以控制Speedcore eFPGA的编程操作,在这种模式下,它充当从控器。CPU模式在1、8、16、32或128位宽的并行接口上运行。

CPU模式是Speedcore eFPGA最快的配置模式,因为它允许eFPGA的配置比特流以最大支持的时钟速率通过128位总线(在其最宽的配置中)进入FCU。所有Speedcore eFPGA配置模式都支持100 MHz的最大时钟速率,因此CPU配置模式中的最大比特流配置数据速率为12.8 Gbits/sec。

串行闪存配置模式

FCU的Speedcore eFPGA串行闪存配置模式允许FCU从SPI串行NOR闪存加载配置比特流。在此模式下,eFPGA为主控器,为SPI闪存提供时钟。与CPU配置模式一样,串行闪存配置模式的最大时钟速率为100 MHz。然而,并非所有串行闪存设备都能在100 MHz下运行。为了适应这种潜在的限制,FCU可以根据ASIC/SoC提供给FCU的时钟,以三种额外的时钟速率驱动闪存的时钟。串行闪存的四种可用时钟速率为:

- 除以1(全速)

- 除以2

- 除以4

- 除以8(默认值)

使用Achronix生成配置比特流时选择时钟速率ACE设计工具。使用ACE GUI的“比特流生成实现选项”部分中的“串行闪存时钟分频器”下拉菜单配置选择。最初在通电时,FCU的串行闪存配置模式使用8分频闪存时钟运行,因为这是最安全的时钟速率,与任何闪存设备兼容。在配置比特流早期嵌入的FCU命令可以增加ACE工具设置的闪存时钟速率,以减少从串行闪存加载配置时的总体配置时间。

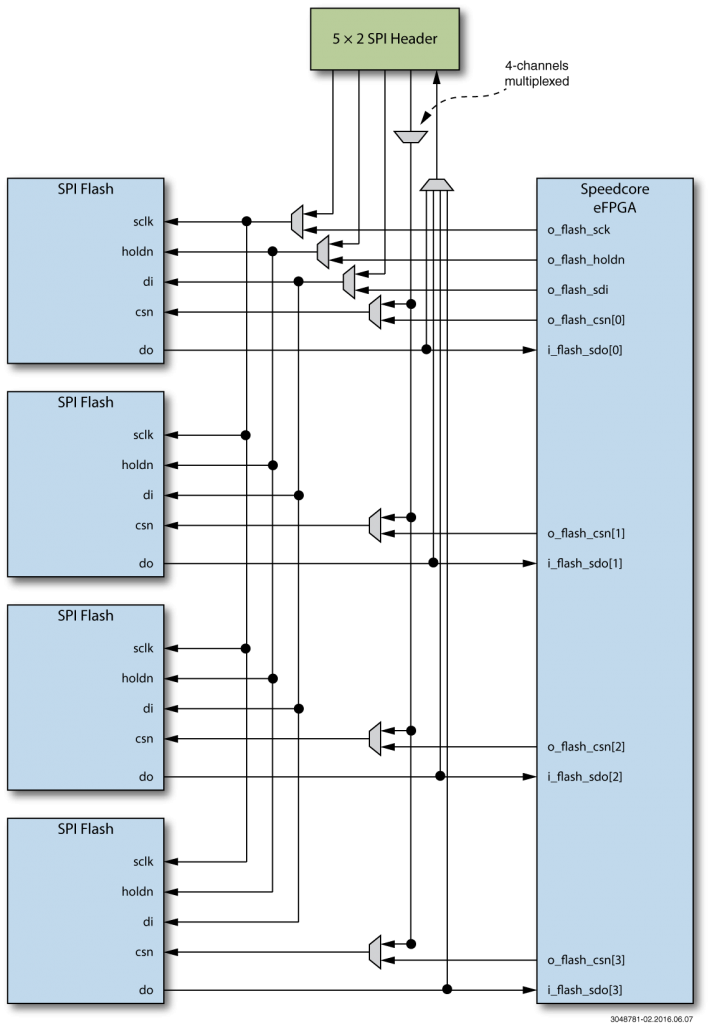

Speedcore eFPGA的串行闪存模式设计用于1位宽的闪存设备。也可以在4位模式下操作,该模式从四个1位宽的闪存设备中的每一个接受一位(如下图所示),这导致配置时间更快,并允许存储更大的配置比特流。

;

JTAG配置模式

FCU的JTAG配置模式采用Speedcore eFPGA的JTAG Tap控制器,该控制器符合IEEE Std 1149.1标准。由于Speedcore JTAG实现用于比特流编程以及实时、系统内控制和观察,因此JTAG TAP控制器在收到适当的数据寄存器(DR)命令后可以控制FCU,而不管eFPGA的配置模式引脚设置如何。

当使用JLOAD DR指令设置为JTAG配置模式时,Speedcore TAP控制器接受ASIC/SoC JTAG TDI数据输入引脚上JTAG端口提供的配置数据,并将其转换为FCU内JTAG逻辑的指令。FCU中的JTAG逻辑使用这些DR指令来组装标准的128位Speedcore配置帧,然后将其转发到FCU状态机,加载eFPGA的配置存储器并配置eFPGA的核心逻辑。

尽管Speedcore JTAG端口可以像eFPGA的其他配置模式一样以最大100 MHz的时钟速率运行,但JTAG配置模式是三种配置模式中最慢的,因为它是一个1位接口,加上添加到配置比特流中的大量通信开销位,以符合JTAG指令协议。

注:本系列博客的第2部分将讨论使用三种Speedcore eFPGA配置模式的配置编程时间。

如需更深入的Achronix Speedcore eFPGA配置技术,包括将多个Speedcore eFPGA内核连接到ASIC/SoC上的一个CPU内核的方法、比特流加密功能和CRC错误检查,请下载 Speedcore配置用户指南 (UG061).